https://chanfifo77.tistory.com/89

[Verilog] 23. AXI - SPI Connection Debugging (1)

https://chanfifo77.tistory.com/87 [Verilog] 21. SPI Debugging (2)https://chanfifo77.tistory.com/86 [Verilog] 20. SPI Debugging(1)발견된 문제점1. 전제 모듈 연결 후, Read 할 때, MISO 값이 간헐적으로 이상하게 나오는 것을 확

chanfifo77.tistory.com

저번에 이어 READ Operation을 작성하겠습니다.

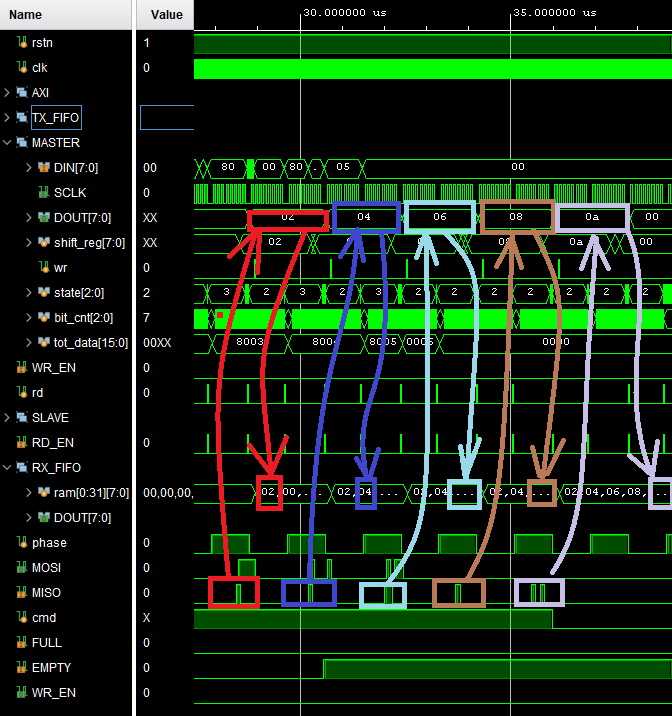

그전에 MISO에서 RX_FIFO의 RAM으로 값이 정상적으로 동작하지 않는 것을 확인하였습니다.

Problem 1.

RX_FIFO RAM 값 오류

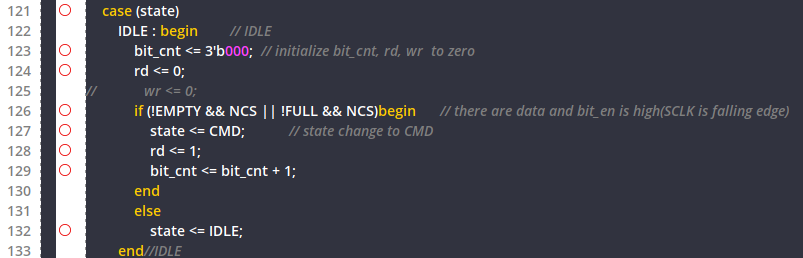

기존 CMD state로 이동하는 코드는

if (!EMPTY && NCS) 였기 때문에 Read 에서는 state가 IDLE에 갇혀있었습니다.

이렇게 되면 rd 신호가 거의 항상 동작하기 때문에 문제가 있을 수 있지만, 저는 FIFO에서 일정 시간 이후 값 변화가 없으면 0으로 초기화 하게 설정을 해두었기 때문에 MOSI로 0의 값만 나가서 동작에서 오류가 있지는 않습니다.

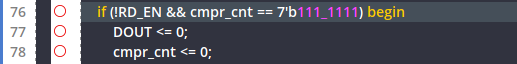

원래 초기화 동작을 하는 cnt는 9비트(512 번) 이었지만 7bit로 변경하면서 사용 CLK를 1/4fh 줄이니 MASTER 동작에서 정상적으로 동작함을 확인하였습니다.

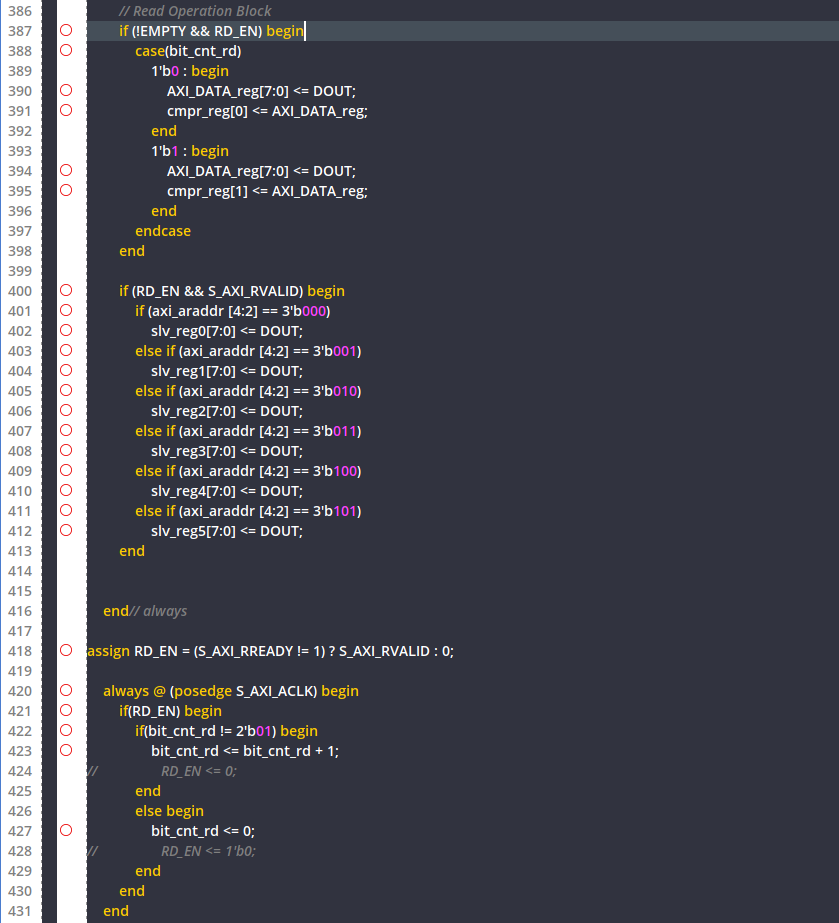

이제 AXI의 Read Operation 을 설계하도록 하겠습니다.

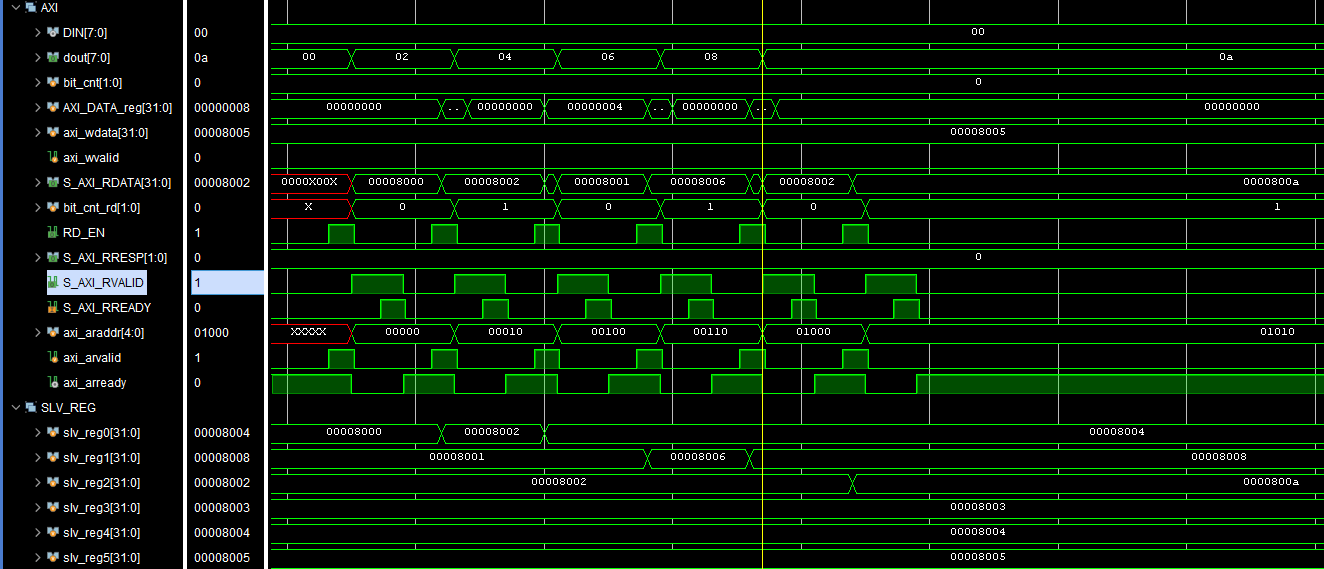

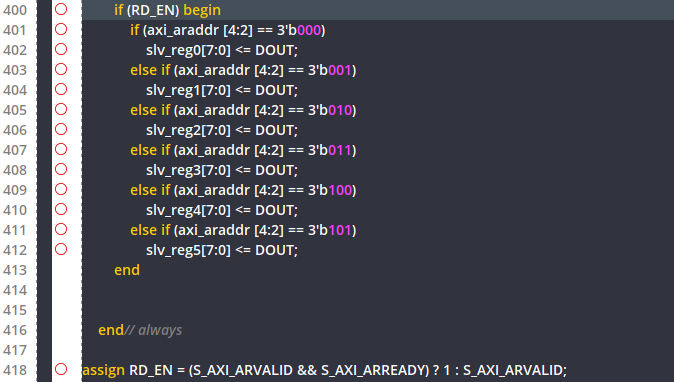

위의 코드를 추가하여 DOUT으로 들어오는 RX_FIFO에 저장된 값을 AXI_Master가 불러오려는 slv_reg에 바로 넣어주면, Handshake가 일어날 때 값이 전송되도록 하는 코드입니다.

// Implement memory mapped register select and read logic generation

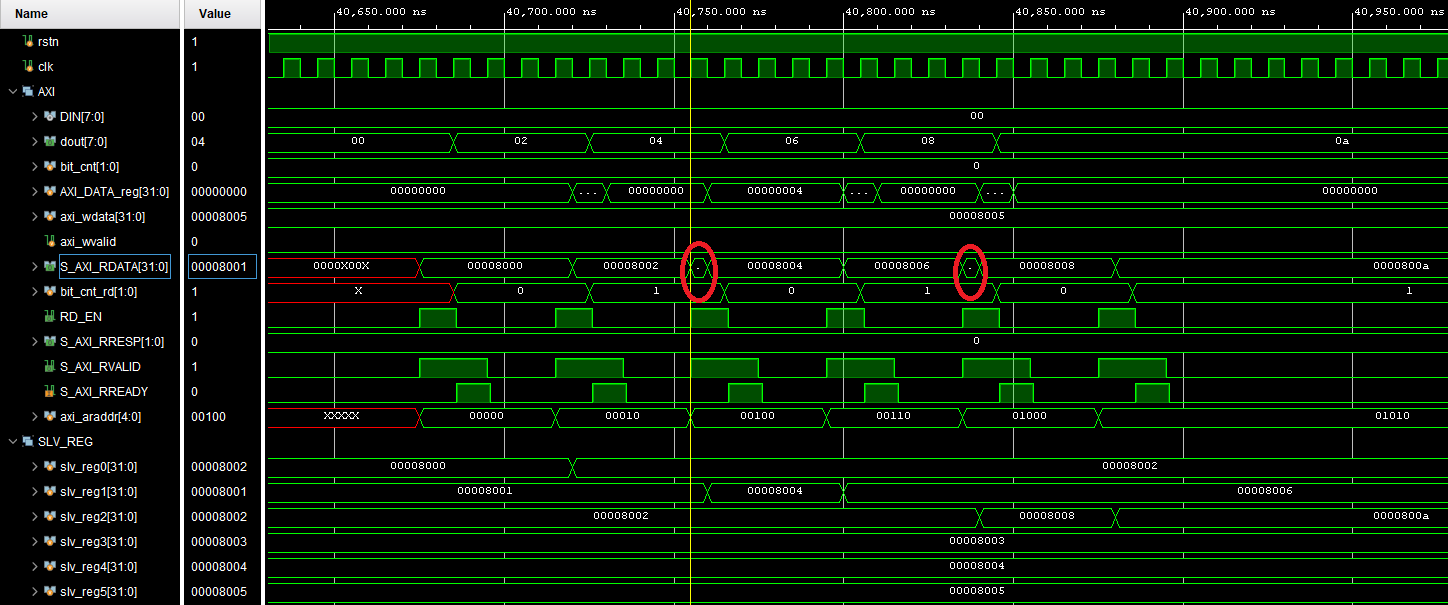

assign S_AXI_RDATA = (axi_araddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] == 2'h0) ? slv_reg0 : (axi_araddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] == 2'h1) ? slv_reg1 : (axi_araddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] == 2'h2) ? slv_reg2 : (axi_araddr[ADDR_LSB+OPT_MEM_ADDR_BITS:ADDR_LSB] == 2'h3) ? slv_reg3 :0;하지만 값이 간헐적으로 다음 slv_reg와 충돌하며 출력됩니다.

하지만 Slave에서 Master로 값이 들어가는건 Hanshake가 일어날 때이기 때문에 당장의 출력에 영향을 미치진 않습니다.

Problem 2.

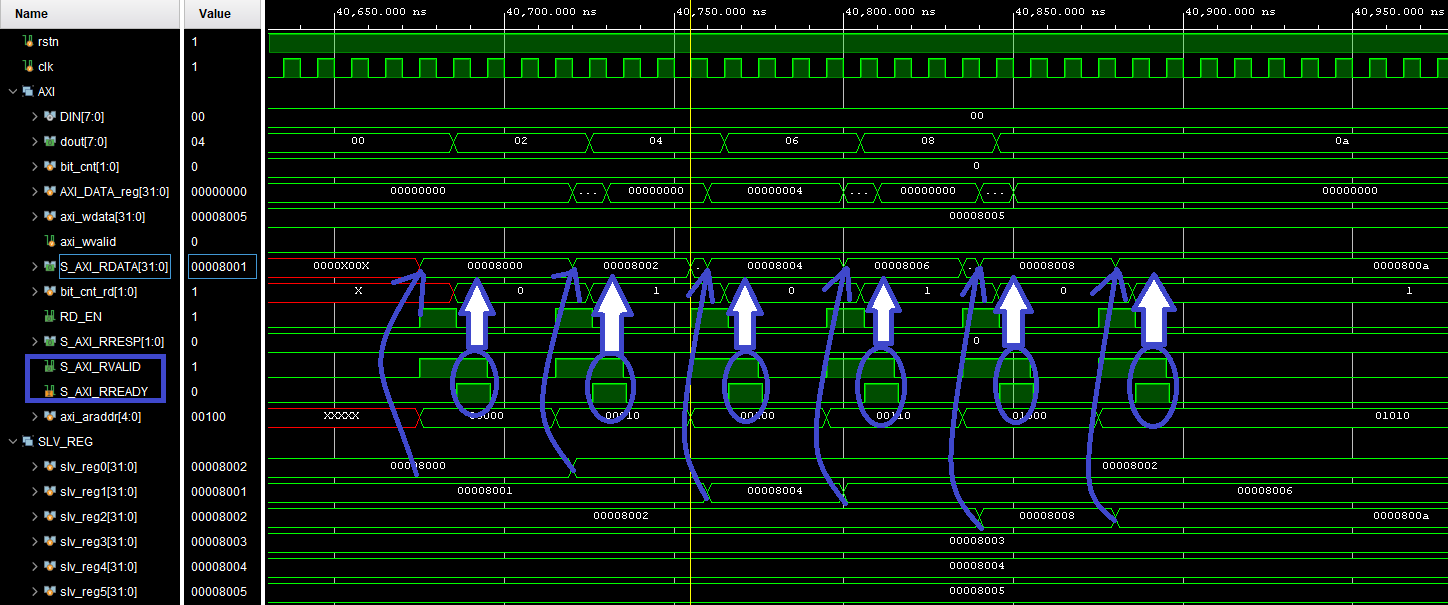

Read Valid 신호시 값 오류.

값이 현재 Testbench 상에서는 출력이 문제가 없지만, Master로 부터 오는 S_AXI_RREADY 신호가 Valid의 앞쪽이라면 잘못된 값이 전송될 수 있다. 그렇기에 RD_EN 신호를 ADDR Handshake와 연결하여 사용하면 이러한 문제점이 아래와 같이 해결된다.

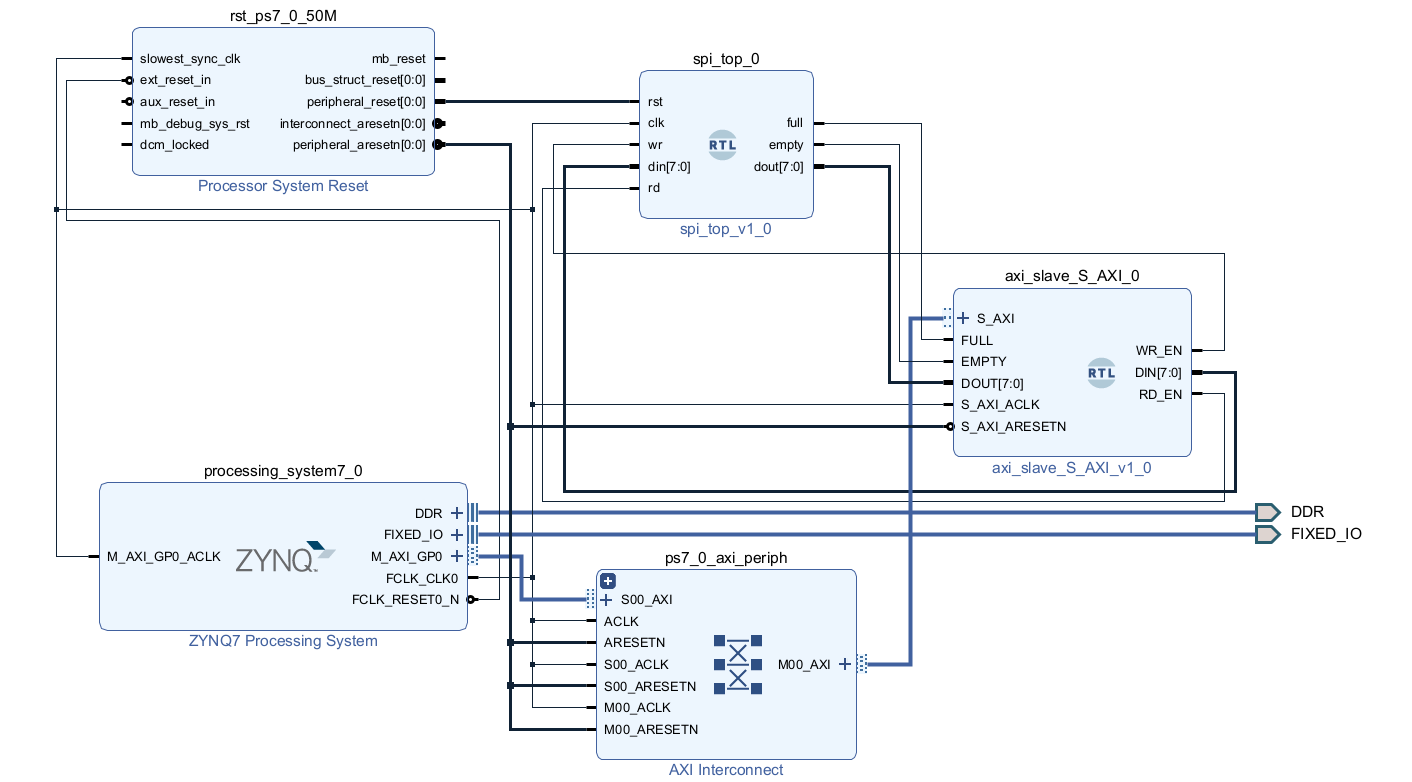

IP Catalog에서 IP와 module을 추가해준다음 작성한 테스트벤치처럼 선들을 연결해준다.

하지만 이번에도 Generate Bitstream을 통과하지 못한다.

추가적인 Debugging은 다음 포스팅에서 작성하도록 하겠습니다.

'Circuit Design > 🔥HDL' 카테고리의 다른 글

| [Verilog] 26. SPI - AXI Portfolio (2) | 2024.08.23 |

|---|---|

| [Verilog] 25. AXI - SPI Connection Debugging (3) (0) | 2024.08.23 |

| [Verilog] 23. AXI - SPI Connection Debugging (1) (0) | 2024.07.23 |

| [Verilog] 22. UART 제작기 (1) (0) | 2024.07.23 |

| [Verilog] 21. SPI Debugging (2) (2) | 2024.07.22 |