https://chanfifo77.tistory.com/87

[Verilog] 21. SPI Debugging (2)

https://chanfifo77.tistory.com/86 [Verilog] 20. SPI Debugging(1)발견된 문제점1. 전제 모듈 연결 후, Read 할 때, MISO 값이 간헐적으로 이상하게 나오는 것을 확인.2. Master에서 RX FIFO로 가는 DOUT의 출력 값 이상 확

chanfifo77.tistory.com

Vivado 에서 제공하는 AXI Example에 기존에 만든 SPI를 연결하는 과정을 담아보겠습니다.

이번 포스팅 목표

1. AXI를 통해 Write 동작 하여 SPI와 연결된 RAM에 저장.

2. AXI를 통해 Write 동작(CMD) 하여 RAM에서 값을 MISO로 출력.

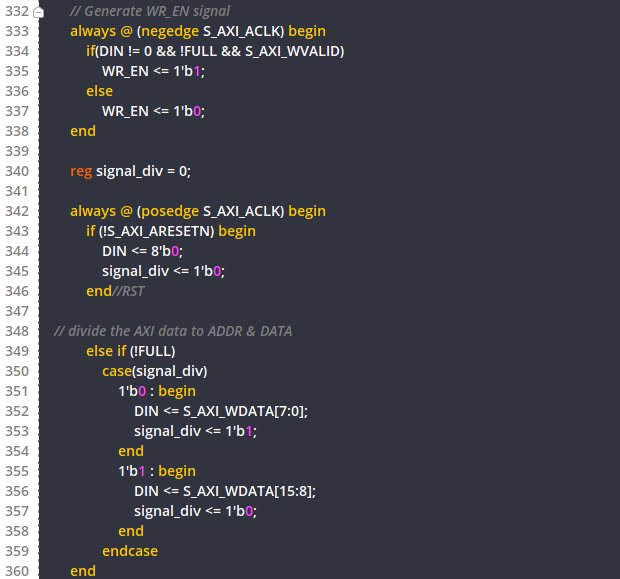

연결할 I/O Port를 추가해주고 DATA를 전송하는 코드를 작성하겠습니다.

현재 연결하는 시뮬레이션에서는 AXI Slave의 내부 Register는 신경쓰지않고 있습니다.

그렇기에 들어오는 DATA를 즉시 SPI의 TX_FIFO로 전달하도록 하는 방향으로 작성하였습니다.

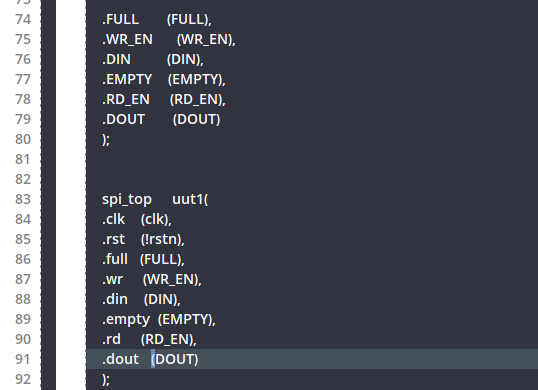

uut로 모듈 인스턴스화 하여 선을 연결하여줍니다.

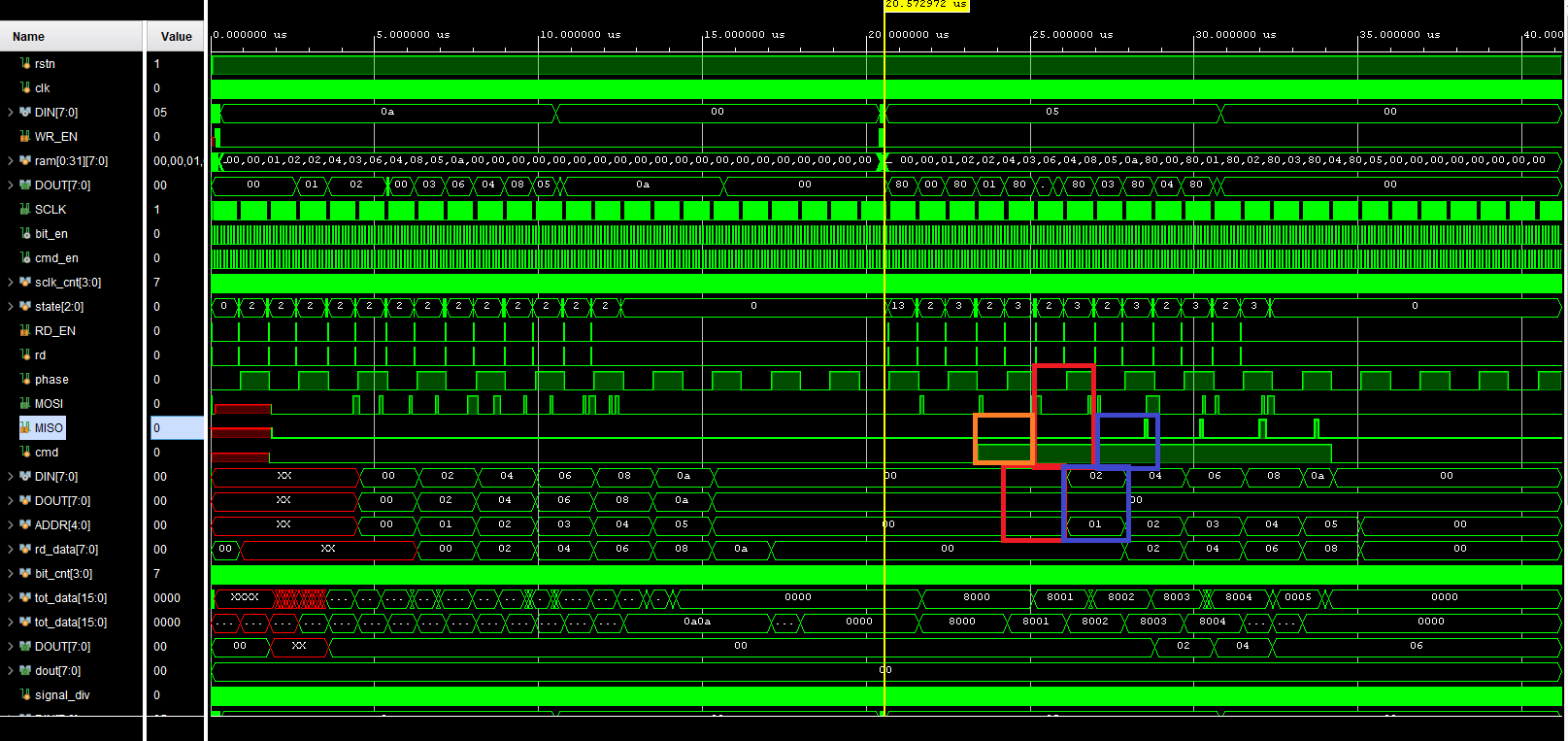

Testbench에서 AXI와 SPI 연결부에서 문제가 생긴 부분을 확인.

Testbench 내에서 DIN, DOUT Port가 선언되지 않아 Default로 1bit로 연결되어 생긴 문제.

연결부 선언 추가.

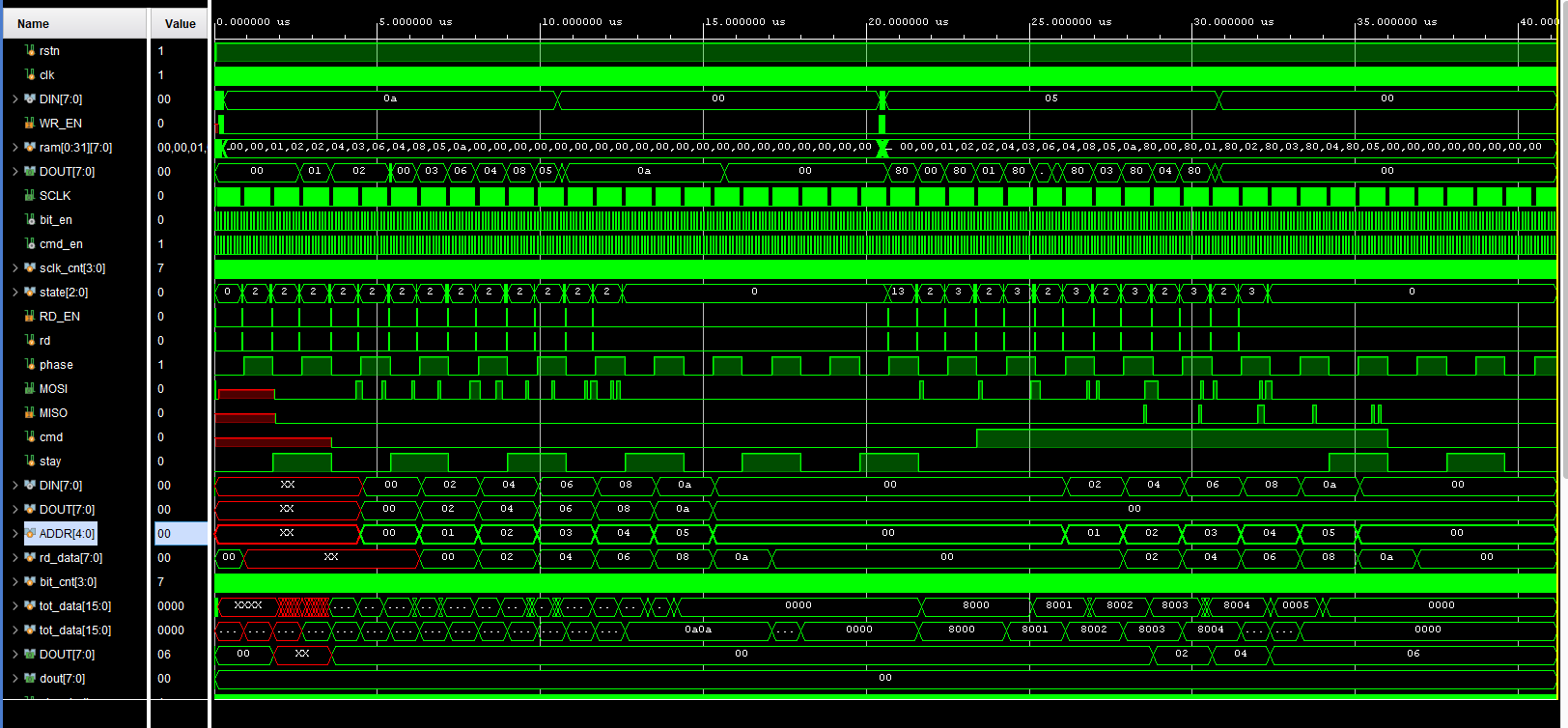

정상적으로 동작

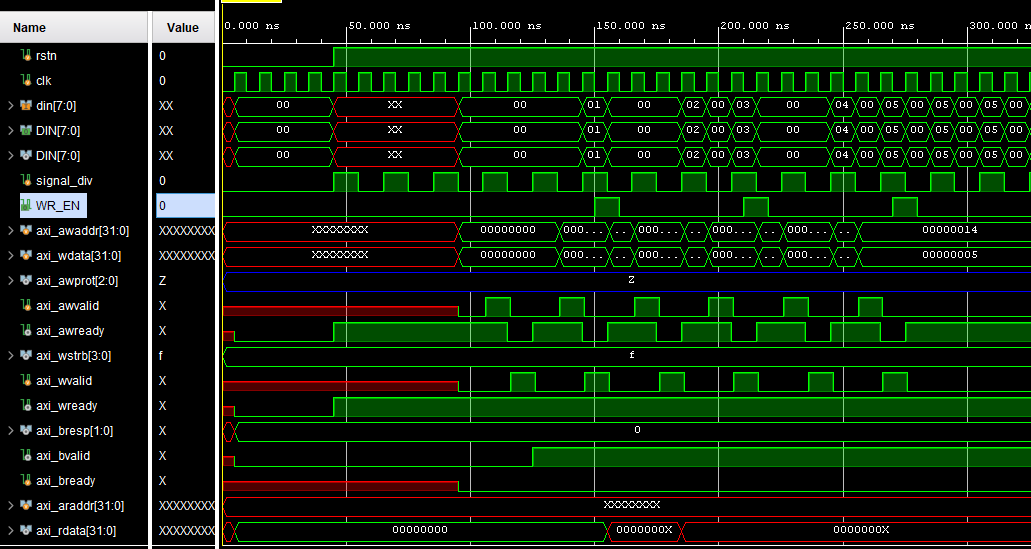

WR_EN 신호가 WDATA에 맞춰 동작하지 않음.

Problem 1.

1/2 phase 만큼 밀려서 TX_FIFO에서 DOUT이 Read 됨.

ADDR과 DATA의 위치가 반전되는 현상.

해결방법.

Phase 시작 값 반전.

Problem 2.

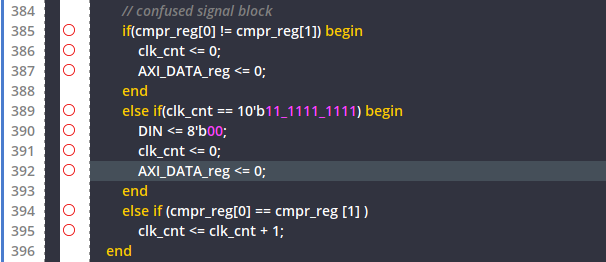

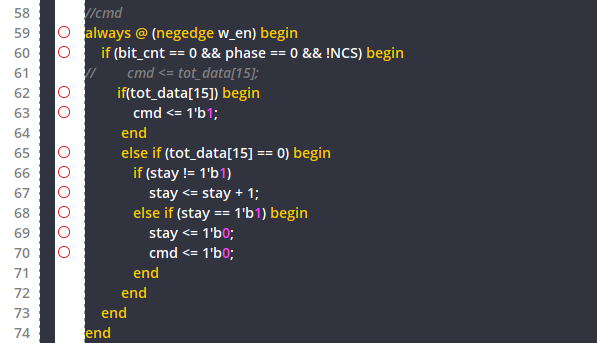

마지막 Write data가 지속해서 TX_FIFO에 남아있어 Read 신호(CMD) 시 MISO로 함께 출력되는 현상.

해결방법.

CLK마다 이전 값과 비교하여 일정 CLK이 증가하면 DIN, DOUT을 초기화하여 이전 DATA가 들어가는 일이 없도록 함.

추가로 MISO로 00 ~ 05 까지 6개의 주소가 전달되었지만 5개만 출력되는 점 확인.

새로운 signal 'stay' 추가하여 cmd를 1 phase동안 연장하여 값이 정상적으로 나오도록 동작.

'Circuit Design > 🔥HDL' 카테고리의 다른 글

| [Verilog] 25. AXI - SPI Connection Debugging (3) (0) | 2024.08.23 |

|---|---|

| [Verilog] 24. AXI - SPI Connection Debugging (2) (0) | 2024.07.26 |

| [Verilog] 22. UART 제작기 (1) (0) | 2024.07.23 |

| [Verilog] 21. SPI Debugging (2) (2) | 2024.07.22 |

| [Verilog] 20. SPI Debugging(1) (0) | 2024.07.18 |