728x90

Counter

counter.v

더보기

'timescale 1ns / 1ps

module counter(

input CLK,

input RST,

output reg [7:0] CNT

);

parameter FULL = 8'd255;

parameter EMPTY = 8'b00;

parameter ADD = 1;

parameter SUBTRACT = 0;

reg up_dn = 1;

always @ (posedge CLK or negedge RST)

begin

if(RST) begin

CNT <= 8'b00;

up_dn <= 1;

end

else begin

case (up_dn)

ADD : begin

if(CNT >= FULL - 1) begin

if(CNT == 8'd254)

CNT <= CNT + 1;

up_dn <= SUBTRACT;

end

else

CNT <= CNT + 1'b1;

end

SUBTRACT : begin

if (CNT == EMPTY + 1) begin

if(CNT == 8'd1)

CNT <= CNT - 1;

up_dn <= ADD;

end

else

CNT <= CNT - 1'b1;

end

endcase

end

end

endmodule

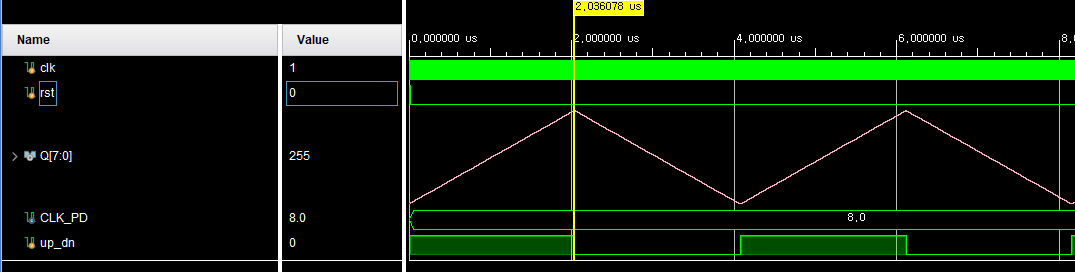

Simulation

counter_tb.v

더보기

'timescale 1ns / 1ps

module counter_tb();

reg clk;

reg rst;

wire [7:0] Q;

parameter CLK_PD = 8.0;

counter uut0(

.CLK (clk),

.RST (rst),

.CNT (Q)

);

always begin

#(CLK_PD/2) clk = ~clk;

end

initial begin

clk <= 0;

rst <= 1'b1;

#10;

rst <= 1'b0;

end

endmodule

my_counter_tb.tcl

더보기

restart

add_force rst -radix hex {1 0ns} {0 5ns}

add_force clk -radix hex {1 0ns} {0 5ns} -repeat_every 10ns

run 6us실행은

Tcl Console 창에

source + 주소 입력.

728x90

'Circuit Design > 🔥HDL' 카테고리의 다른 글

| [Verilog] Verilog를 이용한 AI 설계 응용 및 SoC 설계 (1) (0) | 2024.09.25 |

|---|---|

| [Verilog] 29. 4-bit CPU Project (2) (0) | 2024.08.28 |

| [Verilog] 26. SPI - AXI Portfolio (2) | 2024.08.23 |

| [Verilog] 25. AXI - SPI Connection Debugging (3) (0) | 2024.08.23 |

| [Verilog] 24. AXI - SPI Connection Debugging (2) (0) | 2024.07.26 |