https://n.news.naver.com/article/030/0003187731

'유리기판·2.5D 확보'…550억 규모 차세대 반도체 패키징 R&D 시동

국내 반도체 생태계 최대 약점으로 지목됐던 첨단 패키징 기술 확보 프로젝트가 시작된다. 인공지능(AI)과 같은 차세대 반도체를 구현할 '2.5D와 3D 패키징', 미래 반도체 기판으로 주목받는 '유리

n.news.naver.com

국내 반도체 업계의 약점으로 지목됐던 패키징 기술 확보 프로젝트가 시작됩니다. 차세대 반도체를 구현할 '2.5D와 3D 패키징', 미래 반도체 기판으로 주목받는 '유리기판'이 타깃입니다. 과학기술정보통신부는 2028년까지 총 553억 원을 투입하는 반도체 패키징 사업을 개시했습니다. 2.5D·3D 적층 패키징, 유기기판 소재·공정, 하이드브리드 본딩, 첨단 패키징용 인터포저 소재·공정 기술 개발이 핵심입니다. 이 기사를 보고 저는 오늘 적층 패키징에 대해 다뤄보려고 합니다.

2.5Dㆍ3D 적층 패키징이란?

2.5Dㆍ3D 적층 패키징 방식을 이해하려면 2D 적층 패키징부터 살펴보아야 합니다.

2D 패키징은 2개의 반도체 칩이 수평으로 놓여있는 방식입니다. 지금까지 사용되고 있는 MCM(Multi Chip Module)의 방식이 2D 패키징이라고 할 수 있습니다.

2.5D 패키징 방식은 2D 패키징과 유사하게 보입니다.

하지만 기판과 칩 사이에 인터포저(Interposer) 기판이 존재하여, 이 인터포저 기판 위에 칩을 연결한다는 차이가 있습니다. 그렇다면 왜 2.5D 패키징이 각광받을까요?

정해진 면적의 기판에 많은 양의 칩을 집적하기 위해서 칩 위에 칩을 올릴 수 있다면 효과적이지 않을까요? 기판 위의 공간을 전부 활용했다면 칩 위의 공간을 활용하여 더 많은 칩을 연결하는 방식을 2.5D 패키징이라고 합니다.

대세 칩 적층 방식은 TSV

칩을 적층하는 기술은 칩 적층(Chip Stack, Chip Stack with Wire Bonding)과 실리콘 관통 전극(Through Si Via, TSV, Chip Stack with TSV)으로 나눌 수 있습니다.

칩 적층(Chip Stack, Chip Stack with Wire Bonding) 패키징방식은 패키지를 그대로 적층하는패키지 적층 패키지에 비해서 더 작은 크기의 패키지를 구현할 수 있고 전기적 신호 전달 경로가 짧아 전기적 특성이 우수합니다. 하지만 패키지 테스트 시 한 개의 칩이 불량인 경우 패키지 내의 다른 칩들이 양품이더라도 전체 패키지를 버려야 하므로 테스트 수율에 상대적으로 취약하다는 단점이 존재합니다. 또한 패키지 두께가 두꺼워지는 것을 원하는 고객은 없기 때문에 적층을 한다면 기판을 얇게 만들어야 하는 어려움이 있습니다.

실리콘 관통 전극(Through Si Via, TSV, Chip Stack with TSV)은 실리콘을 뚫어서 전도성 재료로 채운 전극을 의미하며, 칩을 적층하기 위한 기술입니다. 칩을 적층하면서 칩과 칩 또는 기판 연결을 칩에 구멍을 뚫어 금속으로 채워 수직 연결 방식을 사용합니다. 위의 그림처럼 TSV를 이용하면 와이어, 와이어 연결부가 필요 없어지며, 그만큼의 패키지 크기를 줄일 수 있게 됩니다. 또한 Chip Stack 방식은 칩 간 신호를 기판을 거쳐 이용해야 하지만 , TSV는 바로 아래로 신호를 전달할 수 있어 전달 경로 길이의 차이가 커집니다.

HBM은 패키지가 다 완료된 제품이 아닌, 반 패키지 제품입니다. 시스템 업체에 HBM을 보내면 시스템 업체가 인터포저를 나란히 붙인 2.5D 패키지를 만들어줍니다. 이때의 패키지는 일종의 SiP(System in Package)입니다.

SiP(System in Package)

SiP(System in Package)는 모든 시스템을 한 개의 패키지 안에 넣는 것을 말합니다. 현재 기술력으로는 완벽한 SiP를 구현하는 것은 불가능합니다. 그렇기에 지금은 몇 개의 시스템을 하나의 패키지로 구성한 것을 SiP라고 부릅니다. HBM의 경우에는 HBM과 로직칩을 하나의 패키지로 만들어 SiP로 만드는 것을 의미합니다. 또한 쉽게 생각하면 SoC(System on Chip)*과 대비되는 개념이라고 생각하셔도 됩니다.

* SoC(System on Chip) : 시스템을 칩 레벨에서 구현하는 것을 말한다. 모든 시스템을 한 칩 위에 구현하여 SoC라고 부른다.

인터포저(Interposer) : 2.5D 패키지에는 HBM과 로직칩의 I/O범프수가 너무 많아서 기판에 그를 대응하는 패드를 만들 수 없습니다. 그래서 웨이퍼 공정을 통해서 HBM과 로직칩을 대응할 수 있는 패드와 금속 배선을 만들어 HBM, 로직칩을 붙일 수 있게 한 것이 인터포저입니다. 이 인터포저는 TSV로 다시 기판에 직접 연결됩니다.

HBM의 사용에 따라 범프의 수가 너무 많아집니다.(HBM당 보통 5,000개의 마이크로 범프) 그렇기 때문에 HBM 개수만큼 범프에 맞는 많은 수의 패드가 필요합니다. 하지만 실제로는 인터포저 내 HBM과 로직 칩에서 내보내는 대부분의 신호는 로직 내 연산 처리된 신호들입니다. 그래서 실제로는 패키지 밖으로 내보낼 신호가 많지 않습니다. 때문에 대부분의 범프는 인터포저와 연결하고 나갈 신호 일부를 인터포저 내 TSV를 통해 기판으로 내보내면 인터포저와 기판을 연결할 범프 수는 많지 않습니다.

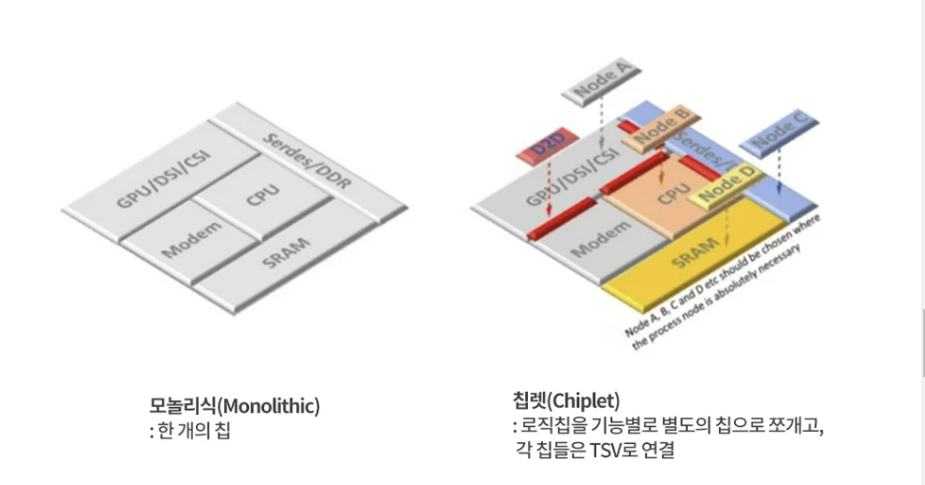

TSV기술을 이용한 칩 수직 적층이 가능해지면서 SiP도 SoC에 견줄만한 전기적 특성을 갖게 되었습니다. SoC 칩의 한쪽 끝에서 반대편 모서리 끝으로 신호를 전달하는 경우, 그 SoC를 9개로 분할한 후 TSV로 적층하면 훨씬 경로가 짧아지는 것을 보여줍니다. 때문에 이 개념을 더욱 발전시킨 칩렛(Chiplet)이란 기술이 최근 많은 관심을 받고 있습니다. 칩렛은 아래 그림처럼 기존의 로직칩을 기능별로 쪼개고, 각 칩들을 TSV로 연결하는 기술입니다.

칩렛의 장점

+) 수율향상

웨이퍼에서 칩 크기가 크면 웨이퍼 수율에서 불리한데, 칩을 쪼개서 만들면 수율이 높아져 제조 비용이 줄어듭니다. SoC로 한 개의 칩으로 구현하는 것보다는 그것을 기능별로 잘라서 SiP로 구현하는 것이 제조 비용상으로도 유리합니다.

+) 개발 효율성 증대

한 개의 칩은 기능을 업그레이드하거나 최신 기술을 적용하고자 할 때 칩 전체를 다시 개발해야 하지만, 칩을 나누어 놓으면 필요 기능을 하는 칩만 업그레이드하거나 최신 기술을 적용해서 개발하면 되므로 개발 기간이 짧아지고, 효율도 높아집니다.

+) 개발 집중성 증가

칩을 기능별로 쪼개어 놓으면 모든 기능의 칩을 직접 개발하지 않아도 됩니다. 핵심 기술에 해당되는 칩만 직접 개발하고, 나머지 칩들은 개발과 구매의 손익을 계산해 볼 수 있는 가능성이 생기고, 접근성과 성능이 좋은 타 기업의 칩을 구매하는 방법을 사용하여 회사의 역량을 핵심 기술 개발에만 몰두하도록 만들 수 있습니다.

글이 너무 길어져서 Chiplet에 대해서는 다음 포스팅에서 다시 다뤄보도록 하겠습니다.

틀린 정보에 관한 지적은 언제나 환영입니다.

'Review > 📰IT' 카테고리의 다른 글

| ㅁ삼성전자의 판도를 바꿀 기술력 후면전력공급(BSPDN)이란? (0) | 2024.03.13 |

|---|