[단독] 삼성전자, 반도체 초미세공정 게임 체인저 ‘후면전력공급’ 기술 상용화 눈앞 - 조선비즈 (chosun.com)

[단독] 삼성전자, 반도체 초미세공정 게임 체인저 ‘후면전력공급’ 기술 상용화 눈앞

단독 삼성전자, 반도체 초미세공정 게임 체인저 후면전력공급 기술 상용화 눈앞 내년 양산하는 2나노 공정에 BSPDN 도입 ARM 코어 면적 최대 19% 줄여 인텔은 연내 도입 목표, TSMC도 개발 중

biz.chosun.com

삼성전자가 개발한 후면전력공급(BSPDN, BackSide Power Delivery Network) 기술을 2 나노 공정에 도입할 예정이라고 합니다.

왜 후면전력공급 기술이 '게임 체인저'라고 불리는지 차근차근 알아보겠습니다.

트랜지스터는 왜 중요한가?

현재의 반도체 기술은 트랜지스터 기술과 매우 밀접합니다. 트랜지스터는 ON/OFF 등의 계산을 수행하는 역할을 하는데, 많은 양의 트랜지스터로 반도체를 구성합니다. 따라서 트랜지스터의 크기가 줄어든다는 말은 곧 반도체의 크기가 줄어든다는 말과 같다고 볼 수 있습니다. 하지만 무작정 작다고 좋은 트랜지스터는 아닐 겁니다 그렇기에 트랜지스터에 대한 조건을 제시했습니다.

좋은 트랜지스터에 대한 기준/조건

삼성전자는 PPA(Performance, Power, Area)를 기준으로 잡고, High Performance, Low Power, Small Area를 목표로 트랜지스터의 기술 발전을 진행하고 있습니다.

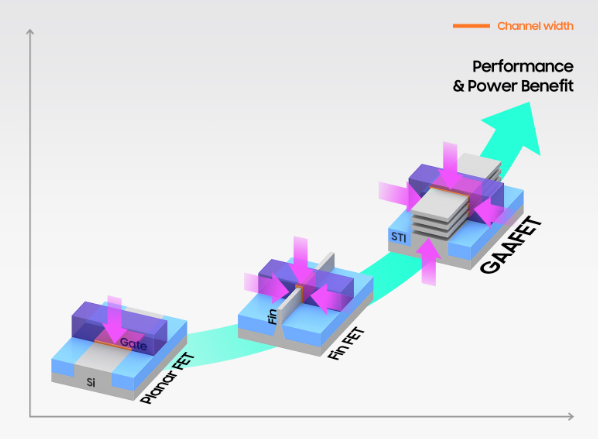

PPA Benefit 향상을 위해 트랜지스터 구조를 변화시키며 최적의 구조를 개발했고, 또 지속적으로 연구 중에 있습니다.

위의 사진의 트랜지스터에 있는 회색 부분이 Channel입니다. channel의 면적이 많아야 전류를 보다 많이 흘려보낼 수 있게 됩니다. 그렇기에 삼성전자에서는 GAAFET(Gate-All-Around Field Effect Transistor)을 개발하여 channel 면적을 극대화하여 트랜지스터 성능을 향상시켰습니다.

결국, DTCO(Design-Technology Co-Optimization)

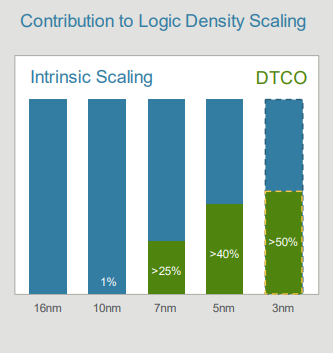

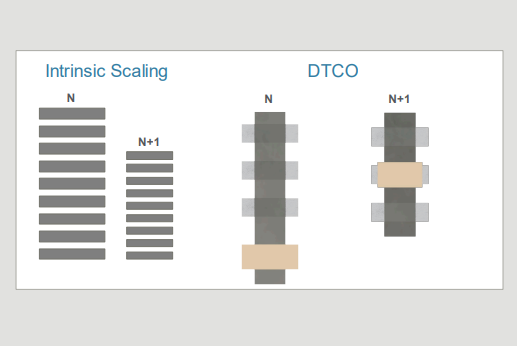

PPA를 모든 부분에서 한 번에 성장시킨다는 것은 어렵습니다. 한 번에 얻을 수 없다면, 현재의 상황에서 가장 최적의 조건을 찾아 발전시키는 수밖에 없습니다. 성능을 떨어트리지 않으면서 크기는 줄일 수 있는 방법, 같은 크기지만 성능을 올릴 수 있는 방법 그리고 작은 힘으로도 같은 성능을 보여줄 수 있는 방법들을 찾아야 합니다. 우리는 공정과 설계의 관점에서 동시에 최적을 찾는 것을 DTCO (Design-Technology Co-Optimization)이라고 부릅니다.

과거와 다르게 단순 공정 미세화보다는 DTCO 방식으로 성능의 향상이 요구되는 것이 현재의 상황입니다.

3 나노 이하의 미세공정의 경우에는 더욱 DTCO의 비중이 커지고 있습니다. 따라서 DTCO를 따라 GAA 등 새로운 구조를 개발하여 성능 개선을 추구하는 것이 현재의 흐름입니다.

그래서 BSPDN이란?

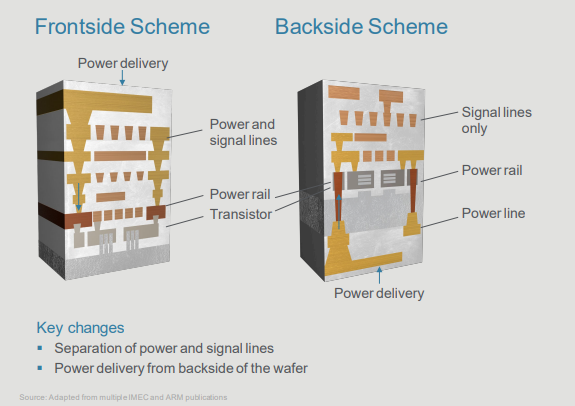

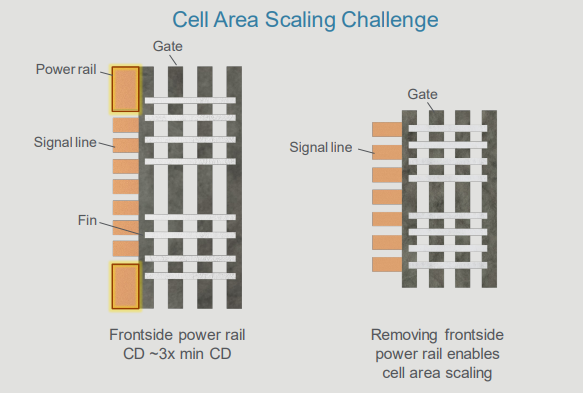

BSPDN(Backside Power Delivery Network) 기술은 트랜지스터 아래의 전원 와이어(일반적으로 전면 공간의 20%를 차지해 왔던 영역)를 칩의 후면으로 이동하고 칩의 전면을 남겨두는 방식입니다. 메탈 배선을 웨이퍼 뒷면에 구현하여, 트랜지스터까지 가는 물리적인 배선의 길이를 줄이고, 셀 면적을 확보할 수 있다는 점이 특징적입니다. 또한 공정의 미세화로 발생했던 회로간섭 문제도 감소시킬 수 있다는 특징도 갖고 있습니다.

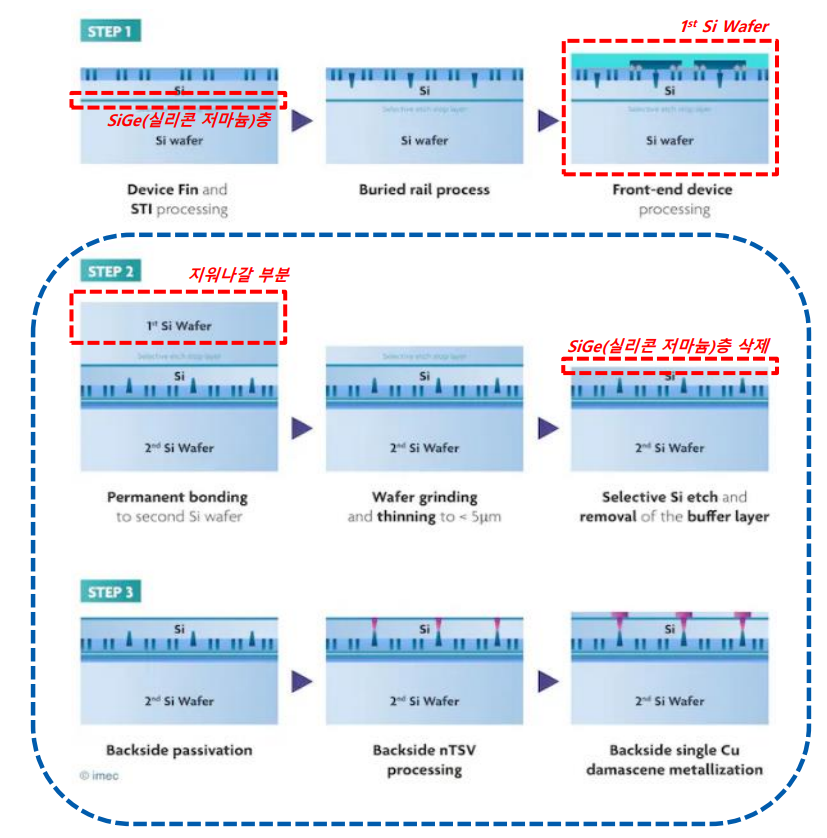

1. BSPDN(Backside Power Delivery Network)는 일반적인 웨이퍼 주요 공정 앞 단과 비슷하게 시작합니다. 300mm Si 웨이퍼 위에 SiGe (향후 Step2에서 Wafer Thinning 시 필요한 식각 정지 층 역할)을 성장시킵니다. 그 위에 Si 캡핑 층을 추가로 성장시키고 마지막으로 Cu로 전면처리를 완료합니다.

2. Carrier Wafer(빈 실리콘 웨이퍼, 2nd Si Wafer로 표기된 부분)가 Interconnect(인터 커넥트) 상단에 접착되고 전체를

뒤집게 되는데, 이때 SiCN-to-SiCN dielectric ‘Fusion Bonding’과 ‘Annealing(약 250도 온도에서 진행)’ 공정으로 마무리하게 되고 이는 BSPDN 기술 구현을 위해서 고도화되어야 할 핵심 공정입니다.

3. 이어서 웨이퍼 바닥(Step 2 기준 그림의 상단부)을 TSV의 끝이 보일 때까지

‘Backside Grinding → Chemical Mechanical Polishing(CMP) → Selective Etching(Oxide Etcher)’

공정을 지속적으로 반복하며 웨이퍼를 얇게 만들어야 합니다. 위 공정을 반복하면 10um 미만으로 웨이퍼를 극도로 얇게 만들게 됩니다.

4. 마지막으로 후면 전력 공급 네트워크를 형성하기 위해 상대적으로 두꺼운 상호 연결 레이어를 구축해야 합니다.

+) 여전히 Bonding 기술의 고도화는 필요하고 , 10nm 이하 수준으로 Wafer 정렬을 요구하기 때문에, Overlay 계측에 대한 중요성도 동시에 높아질 가능성을 배제할 수 없을 것으로 예상됩니다.

삼성전자는 1.7 나노 공정부터 BSPDN 기술을 도입할 것으로 알려졌지만, 이르면 2 나노 공정 양산이 시작되는 내년부터 해당 기술을 도입한다는 내용도 위의 기사에 포함되어 있습니다

현재 BSPDN의 선두주자로 평가받는 Intel은 PC용 Meteor Lake 칩에 BSPDN 기술을 적용하여 저전력으로 빠르게 작동 가능한 칩에 대한 양산 능력을 확보하였으며, 2026년을 목표로 2 나노 공정인 20A를 대상으로 반도체를 양산할 계획이라고 합니다. TSMC 역시 2 나노 이하 공정에서 이 기술을 적용할 계획이며, 2026년을 목표로 개발 중이라고 합니다.

반도체 미세화 공정기술의 발전으로 DTCO의 중요성이 부각되고 있습니다. BSPDN 기술을 성공적으로 개발하여 삼성전자 BSPDN의 선두주자를 탈환하기를 기원합니다.

참조 : 유안타증권 2024 반도체 전망 (https://file.myasset.com/sitemanager/upload/2023/1128/231850/20231128231850823_0_ko.pdf)

'Review > 📰IT' 카테고리의 다른 글

| 차세대 반도체, 2.5Dㆍ3D 패키징 / 유리기판 / 본딩 으로 잡는다. (1) | 2024.03.14 |

|---|