728x90

전가산기

기존에 만들어둔 반가산기를 사용합니다.

Create Source로 새로운 디자인으로 전가산기를 만들면 두 개의 Design Source가 구성되어 있는 모습을 확인 할 수있습니다.

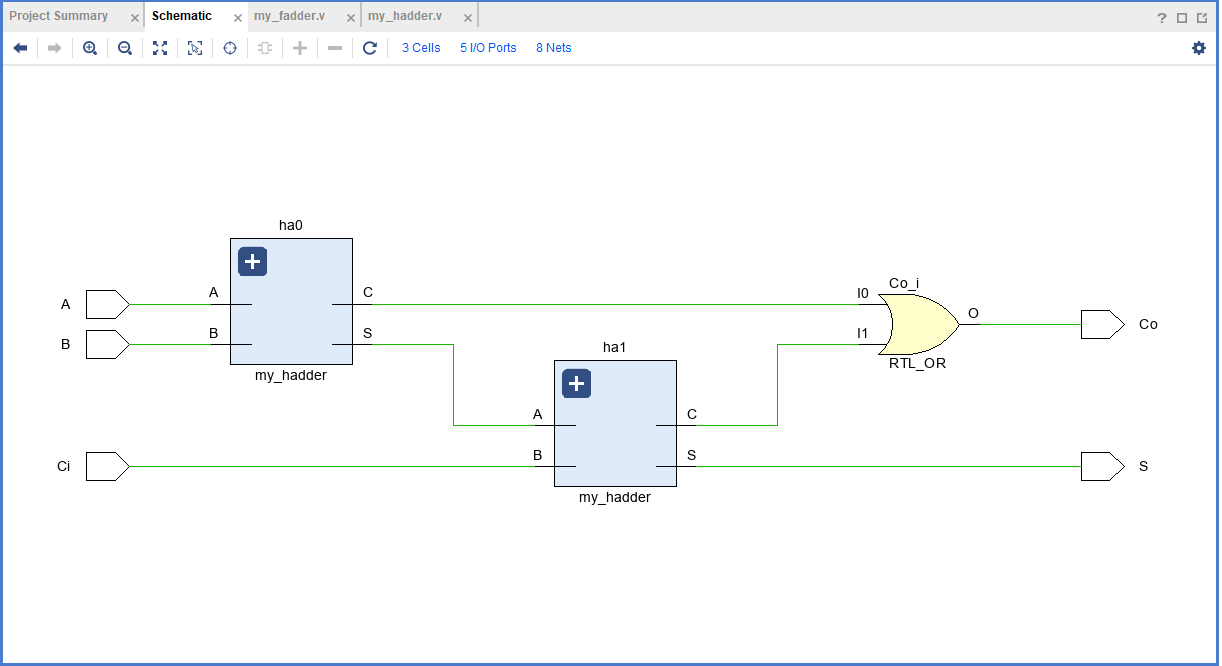

그 후 Create된 파일에 Verilog 코드를 위와 같이 작성합니다. Full adder는 Half adder 2개와 1개의 OR로 이루어져 있기 때문에 그점을 이용하여 코드를 작성할 것입니다.

코드 작성 후 저장을 하면 Source의 디렉토리가 변경된 모습을 확인할 수 있습니다.

Open Elaborated Design을 하면 위 사진과 같이 Half Adder 두개와 OR Gate로 이루어진 Full Adder를 확인 할 수 있습니다.

Run Synthesis 에서 Open Synthesized Design을 선택합니다.

Cora z7에 정상적으로 동작되는 것을 확인 할 수 있습니다.

728x90

'Circuit Design > 🔥HDL' 카테고리의 다른 글

| [Verilog] 4. 1 Sec Counter- (Cora-z7) (0) | 2024.04.01 |

|---|---|

| [Verilog] 3. Counter / Testbench- (Cora-z7) (0) | 2024.04.01 |

| [Verilog] 2. 2Bit Adder - (Cora-z7) (0) | 2024.03.29 |

| [Verilog] 0. VIVADO project 만들기 - 2(Cora-z7) (0) | 2024.03.19 |

| [Verilog] 0. VIVADO project 만들기 - 1(Cora-z7) (1) | 2024.03.19 |