모든 HDLBits 포스팅은 Ligth Theme을 권장합니다.

(왼쪽 메뉴 하단)

문제는 반드시 HDLBits를 참고하세요! 보다 자세하게 적혀있습니다.

https://hdlbits.01xz.net/wiki/Module

Module - HDLBits

hdlbits.01xz.net

Modules

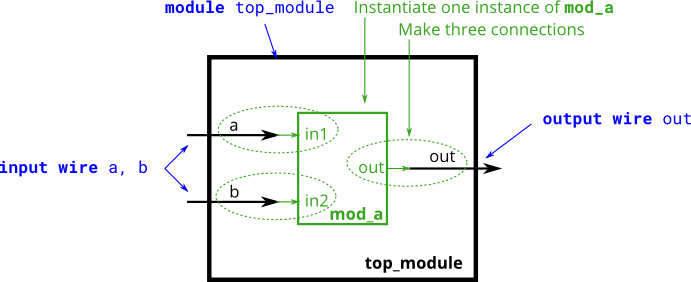

In this exercise, create one instance of module mod_a, then connect the module's three pins (in1, in2, and out) to your top-level module's three ports (wires a, b, and out). The module mod_a is provided for you — you must instantiate it.

이 문제에선 mod_a의 모듈 인스턴스 하나를 만들고, 모듈 핀 3개 (in1, in2, 그리고. out)를 최상위 모듈의 3개 포트(wires)에 연결합니다. a, b, 그리고. out). mod_a 모듈은 주어집니다.

module mod_a ( input in1, input in2, output out );

// Module bodySolution ↓

module top_module ( input a, input b, output out );

mod_a uut0 (.in1(a), .in2(b), .out(out)); // by name

//mod_a uut0 (a, b, out); //by position

endmodule

Module을 Port에 연결하는 두 가지 방법

1) By Position(위치로 인스턴스)

mod_a instance1 ( wa, wb, wc );

위처럼 작성했다고 하면 mod_a의 in1은 wa로, in2는 wb로, out은 wc로 인스턴스화한다는 의미.

※ module 내부에서 port 위치 수정 시 인스턴스는 초기화 된다.

2) By name (이름으로 인스턴스)

mod_a instance2 ( .out(wc), .in1(wa), .in2(wb) );

위처럼 작성하면 각각의 Port를 인스턴스하기 때문에 위치와 상관없이 가능하다.

이 방법이 헷갈릴 일 없고 더 좋을 듯

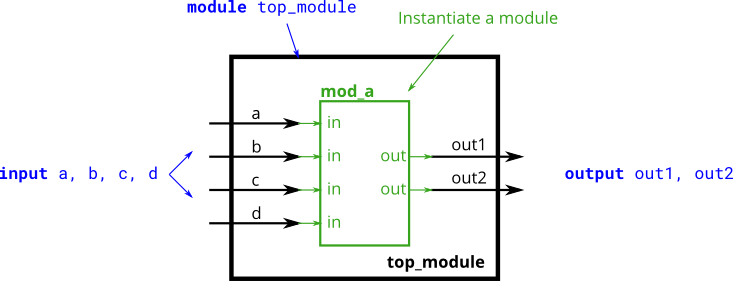

Connecting Ports By Position

You are given a module named mod_a that has 2 outputs and 4 inputs, in that order. You must connect the 6 ports by position to your top-level module's ports out1, out2, a, b, c, and d, in that order.

이름이 지정된 모듈이 제공됩니다. mod_a는 2개의 출력과 4개의 입력을 순서대로 가지고 있습니다. 위치별로 6개의 포트를 최상위 모듈의 포트에 연결해야 합니다( out1, out2, a, b, c, d 순서대로 ).

module mod_a ( output, output, input, input, input, input );Solution ↓

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a uut0 (out1, out2, a, b, c, d);

endmodulemod_a 보고 순서 맞춰서

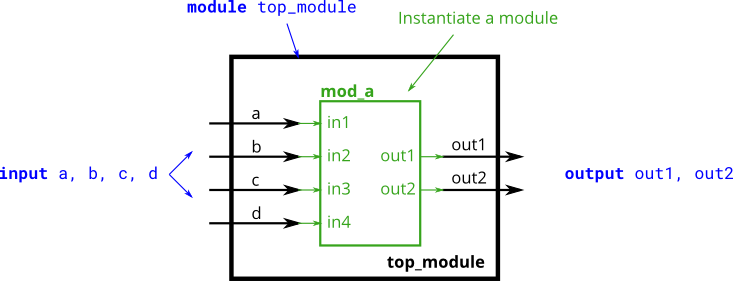

Connecting Ports By Name

You are given a module named mod_a that has 2 outputs and 4 inputs, in some order. You must connect the 6 ports by name to your top-level module's ports:

mod_a는 순서대로 2개의 출력과 4개의 입력을 가지고 있습니다. 이름별로 6개의 포트를 최상위 모듈의 포트에 연결해야 합니다.

| Port in mod_a | Port in top_module |

| output out1 | out1 |

| output out2 | out2 |

| input in1 | a |

| input in2 | b |

| input in3 | c |

| input in4 | d |

module mod_a ( output out1, output out2, input in1, input in2, input in3, input in4);Solution ↓

module top_module (

input a,

input b,

input c,

input d,

output out1,

output out2

);

mod_a uut0 (.in1(a), .in2(b), .in3(c), .in4(d), .out1(out1), .out2(out2));

endmodulemod_a uut0 (.a(b));

mod_a uut0 (.a를(b라고 부를 거야))

Three Modules

You are given a module my_dff with two inputs and one output (that implements a D flip-flop). Instantiate three of them, then chain them together to make a shift register of length 3. The clk port needs to be connected to all instances.

주어진 모듈인 my_dff (D 플립플롭을 구현하는)는 두 개의 입력과 한 개의 출력이 있습니다. 그 중 세 개를 인스턴스화한 다음 체인으로 연결하여 길이 3의 시프트 레지스터를 만듭니다. 그 clk 포트를 모든 인스턴스에 연결해야 합니다.

module my_dff ( input clk, input d, output q );Solution ↓

module top_module ( input clk, input d, output q );

wire a, b;

my_dff uut0(.clk(clk), .d(d), .q(a));

my_dff uut1(.clk(clk), .d(a), .q(b));

my_dff uut2(.clk(clk), .d(b), .q(q));

endmodule

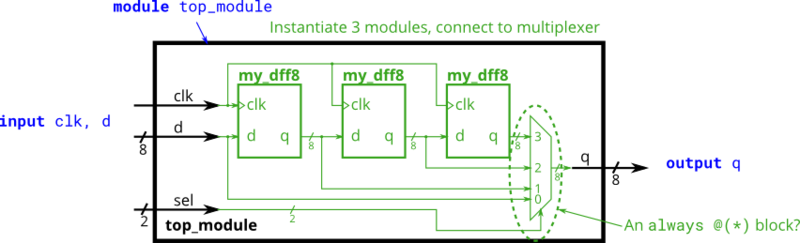

Modules and Vectors

You are given a module my_dff8 with two inputs and one output (that implements a set of 8 D flip-flops). Instantiate three of them, then chain them together to make a 8-bit wide shift register of length 3. In addition, create a 4-to-1 multiplexer (not provided) that chooses what to output depending on sel[1:0]: The value at the input d, after the first, after the second, or after the third D flip-flop. (Essentially, sel selects how many cycles to delay the input, from zero to three clock cycles.)

주어진 모듈 my_dff8 (8D 플립플롭 세트를 구현하는)은 두 개의 입력과 한 개의 출력이 있습니다. 그 중 3개를 인스턴스화한 다음 체인으로 연결하여 길이 3의 8-bit 와이드 시프트 레지스터를 만듭니다. 또한 sel[1:0]에 따라 출력할 값을 선택하는 4x1 멀티플렉서(주어지지 않습니다. always 문을 활용해 만들어보세요.)를 만듭니다. 값은 입력 d 후, 첫 번째 후, 두 번째 후 또는 세 번째 D 플립플롭 후의 값(기본적으로 sel은 입력을 지연시킬 cycle 수를 0~3 clk cycle로선택합니다.)

module my_dff8 ( input clk, input [7:0] d, output [7:0] q );Solution ↓

module top_module (

input clk,

input [7:0] d,

input [1:0] sel,

output [7:0] q

);

wire [7:0] a, b, c;

my_dff8 uut0(.clk(clk), .d(d), .q(a));

my_dff8 uut1(.clk(clk), .d(a), .q(b));

my_dff8 uut2(.clk(clk), .d(b), .q(c));

always @ (sel) begin

if(sel == 2'b00) q <= d;

else if (sel == 2'b01) q <= a;

else if (sel == 2'b10) q <= b;

else if (sel == 2'b11) q <= c;

end

endmodule

Adder 1

You are given a module add16 that performs a 16-bit addition. Instantiate two of them to create a 32-bit adder. One add16 module computes the lower 16 bits of the addition result, while the second add16 module computes the upper 16 bits of the result, after receiving the carry-out from the first adder. Your 32-bit adder does not need to handle carry-in (assume 0) or carry-out (ignored), but the internal modules need to in order to function correctly. (In other words, the add16 module performs 16-bit a + b + cin, while your module performs 32-bit a + b).

주어진 모듈 add16는 16-bit 덧셈을 수행합니다. 그 중 두 개를 인스턴스화하여 32-bit adder를 만듭니다. add16 모듈 하나는 덧셈 결과의 하위 16-bit를 계산하고, 두 번째 add16 모듈은 첫 번째 adder로부터 carry-out 받은 후 결과의 상위 16bit를 계산합니다. 32-bit adder는 carry-in(0으로 가정)이나 carry-out(무시)을 처리할 필요가 없지만, 내부 모듈은 올바르게 작동하기 위해 필요합니다. (즉, add16 모듈은 16-bit a + b + cin을 수행하는 반면 모듈은 32-bit a + b)를 수행합니다.

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );Solution ↓

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire [15:0] sum_hi, sum_lo;

wire cout;

assign sum = {sum_hi, sum_lo};

add16 add0(.a(a[15:0]), .b(b[15:0]), .cin(1'b0), .cout(cout), .sum(sum_lo));

add16 add1(.a(a[31:16]), .b(b[31:16]), .cin(cout), .sum(sum_hi));

endmodule

Adder 2

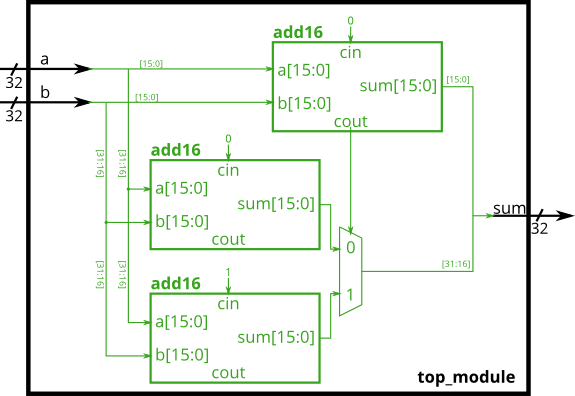

Connect the add16 modules together as shown in the diagram below.

Within each add16, 16 full adders (module add1, not provided) are instantiated to actually perform the addition. You must write the full adder module

Recall that a full adder computes the sum and carry-out of a+b+cin.

In summary, there are three modules in this design:

- top_module — Your top-level module that contains two of...

- add16, provided — A 16-bit adder module that is composed of 16 of...

- add1 — A 1-bit full adder module.

add16 제공된 모듈을 가지고 위의 다이어그램처럼 연결하세요.

각각의 내부에 add16, 16개의 full adder(module add1을 사용, 주어지지 않음.)는 실제로 덧셈을 수행하기 위해 인스턴스화됩니다. 다음 선언이 있는 전체 덧셈 모듈을 작성해야 합니다.

전가산기(Full Adder)는 a+b+cin의 합과 carry-out을 계산합니다.

요약하면, 이 설계에는 3개의 모듈이 있습니다.

• top_module - 2개의 모듈로 구성된 top-level module

• add16, provided - 16개의 add1로 구성된 16-bit-adder

• add1 - 1-bit full adder module

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );module add1 ( input a, input b, input cin, output sum, output cout );Solution ↓

module top_module (

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire i, j;

add16 adder_up (

.a(a[15:0]),

.b(b[15:0]),

.cin(0),

.sum(sum[15:0]),

.cout(i)

);

add16 adder_down (

.a(a[31:16]),

.b(b[31:16]),

.cin(i),

.sum(sum[31:16]),

.cout(j)

);

endmodule

// module add_16 (

// input [15:0] a,

// input [15:0] b,

// input cin,

// output [15:0] sum,

// output cout

// );

//

// wire [14:0] carry;

//

// add1 bit0 (.a(a[0]), .b(b[0]), .cin(cin), .sum(sum[0]), .cout(carry[0]));

// add1 bit1 (.a(a[1]), .b(b[1]), .cin(carry[0]), .sum(sum[1]), .cout(carry[1]));

// add1 bit2 (.a(a[2]), .b(b[2]), .cin(carry[1]), .sum(sum[2]), .cout(carry[2]));

// add1 bit3 (.a(a[3]), .b(b[3]), .cin(carry[2]), .sum(sum[3]), .cout(carry[3]));

// add1 bit4 (.a(a[4]), .b(b[4]), .cin(carry[3]), .sum(sum[4]), .cout(carry[4]));

// add1 bit5 (.a(a[5]), .b(b[5]), .cin(carry[4]), .sum(sum[5]), .cout(carry[5]));

// add1 bit6 (.a(a[6]), .b(b[6]), .cin(carry[5]), .sum(sum[6]), .cout(carry[6]));

// add1 bit7 (.a(a[7]), .b(b[7]), .cin(carry[6]), .sum(sum[7]), .cout(carry[7]));

// add1 bit8 (.a(a[8]), .b(b[8]), .cin(carry[7]), .sum(sum[8]), .cout(carry[8]));

// add1 bit9 (.a(a[9]), .b(b[9]), .cin(carry[8]), .sum(sum[9]), .cout(carry[9]));

// add1 bit10 (.a(a[10]), .b(b[10]), .cin(carry[9]), .sum(sum[10]), .cout(carry[10]));

// add1 bit11 (.a(a[11]), .b(b[11]), .cin(carry[10]), .sum(sum[11]), .cout(carry[11]));

// add1 bit12 (.a(a[12]), .b(b[12]), .cin(carry[11]), .sum(sum[12]), .cout(carry[12]));

// add1 bit13 (.a(a[13]), .b(b[13]), .cin(carry[12]), .sum(sum[13]), .cout(carry[13]));

// add1 bit14 (.a(a[14]), .b(b[14]), .cin(carry[13]), .sum(sum[14]), .cout(carry[14]));

// add1 bit15 (.a(a[15]), .b(b[15]), .cin(carry[14]), .sum(sum[15]), .cout(cout));

//

// endmodule

module add1 (

input a,

input b,

input cin,

output sum,

output cout

);

assign sum = a ^ b ^ cin;

assign cout = (a & b) | (a & cin) | (b & cin);

endmodule문제를 잘 읽기!!

16bit adder가 이미 내부까지 다 만들어져 있는 상태.

주어진 회로는 건들지 말고 그대로 쓰자.

Carry-Select Adder

In this exercise, you are provided with the same module add16 as the previous exercise, which adds two 16-bit numbers with carry-in and produces a carry-out and 16-bit sum. You must instantiate three of these to build the carry-select adder, using your own 16-bit 2-to-1 multiplexer.

이 문제에서는 전에 주어진 것과 동일한 add16으로, 16-bit 숫자 2개를 carry-in으로 추가하고 carry-out과 16-bit 합을 생성합니다. 16-bit 2x1 멀티플렉서를 이용하여 Carry-Select Adder를 구축하려면 이 중 3개를 인스턴스화해야 합니다.

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );Solution ↓

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire mux;

wire [15:0] in1, in2;

// lower bits

add16 adder1 (a[15:0], b[15:0], 1'b0, sum[15:0], mux);

// upper bits

add16 adder2 (a[31:16], b[31:16], 1'b0, in1);

add16 adder3 (a[31:16], b[31:16], 1'b1, in2);

always @ (mux)begin

if(mux == 0) begin

sum[31:16] <= in1;

end

else if (mux == 1) begin

sum[31:16] <= in2;

end

end

endmodule

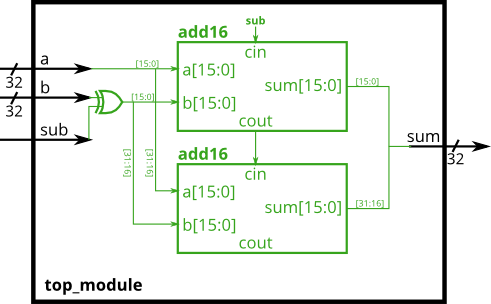

Adder Subtractor

Build the adder-subtractor above.

You are provided with a below 16-bit adder module, which you need to instantiate twice:

위의 가감산기를 구축하세요. 아래의 16-bit adder 모듈이 제공됩니다. 이 모듈을 두 번 인스턴스화 해야합니다.

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );Solution ↓

module top_module(

input [31:0] a,

input [31:0] b,

input sub,

output [31:0] sum

);

wire [31:0] sub_32 = {32{sub}};

assign k = b ^ sub_32;

wire [31:0] k;

wire out_in;

add16 subtractor1 (a[15:0], k[15:0], sub, sum[15:0], out_in);

add16 subtractor2 (a[31:16], k[31:16], out_in, sum[31:16]);

endmodule

여기부터 슬슬 재밌어지네요. 오늘 Adder2 부분에서 문제를 주의 깊게 안 봐서 시간이 오래 걸렸습니다.

틀린 부분에 대한 지적은 언제나 환영입니다.

모든 HDLBIts 포스팅은 Light Theme을 권장합니다.

'Circuit Design > 🚀HDLBits' 카테고리의 다른 글

| [HDLBits] 5. Verilog Language - More Verilog Features (0) | 2024.07.11 |

|---|---|

| [HDLBits] 4. Verilog Language - Procedures (0) | 2024.07.08 |

| [HDLBits] 2. Verilog Language - Vectors (0) | 2024.07.07 |

| [HDLBits] 1. Verilog Language - Basics (0) | 2024.07.07 |

| [HDLBits] 0. Getting Started (0) | 2024.07.07 |