https://github.com/Xilinx/XilinxBoardStore

GitHub - Xilinx/XilinxBoardStore

Contribute to Xilinx/XilinxBoardStore development by creating an account on GitHub.

github.com

위 링크를 들어가서 Code > Download Zip으로 파일을 다운로드 받아줍니다.

다운로드 된 파일을 압축 해제 한 후, Board에서 원하는 Device를 선택합니다.

저는 Digilent의 Cora-Z7-07s를 선택했습니다. 해당 폴더를 선택 후

C:\Xilinx\Vivado\2023.2\data\xhub\boards\XilinxBoardStore\boards

위의 위치에 붙여넣기 해줍니다.

Vivado

이제 Vivado를 실행 시킨 후, Create Project를 진행하며 Default Part에서 Cora-Z7-07S를 선택하여 진행합니다.

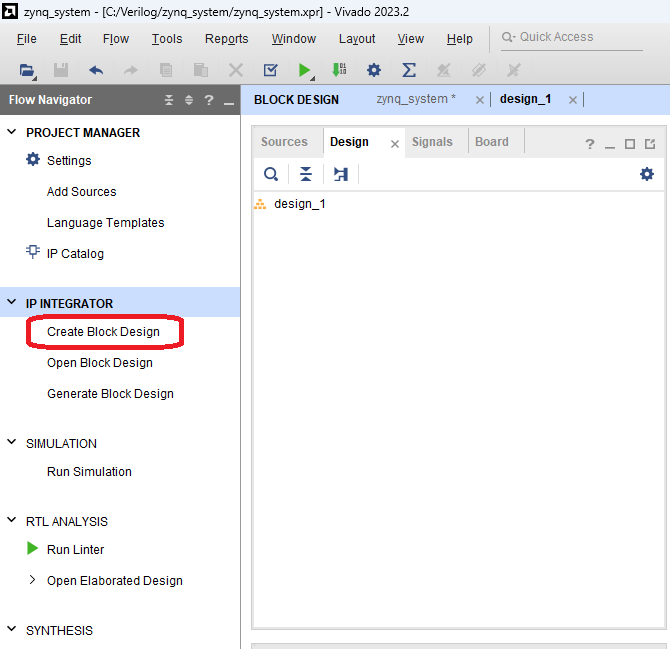

Create Block Design을 실행한 후 Diagram에서 +모양 Add IP를 클릭합니다.

저는 Zynq7 Processing System을 추가하겠습니다.

위처럼 Zynq7 Processing System이 Load된 모습을 확인 할 수 있습니다.

Unit을 더블클릭해 설정에 들어온 후 USB를 해제해줍니다.

처음 Block과 다르게 USBIND_0가 사라진 모습을 확인 할 수 있습니다.

포트 쪽에 마우스 포인터를 가져다 놓은 후 연필모양으로 변경된 후에, 좌클릭으로 드래그하여 움직이면 선을 연결 할 수 있습니다.

그 후 Generate Bitstream을 진행합니다.

Export H/W를 통해서 wrapper 파일을 저장해줍니다. 완료되면 Vivado를 종료하여도 됩니다.

Vitis

이제 Vitis를 실행합니다.

기존에 Zynq_system을 만든 위치에 platform을 만듭니다.

wrapper파일을 불러와 Hardware Design으로 설정하고

단계를 마무리하면

위처럼 결과가 보입니다.

예제를 불러와줍니다.

어떤 플랫폼을 선택할 것인지 결정하는 단계입니다.

'Circuit Design > 🔥HDL' 카테고리의 다른 글

| [Verilog] 14. AXI Read / Handshake (0) | 2024.06.27 |

|---|---|

| [Verilog] 13. AXI(Advanced eXtensible Interface) (0) | 2024.06.25 |

| [Verilog] Vivado Setting [Dark Theme(Vivado 다크모드)] (0) | 2024.06.10 |

| [Verilog] 12. UART(3) TX (0) | 2024.06.10 |

| [Verilog] 11. UART(2) (0) | 2024.06.03 |