디지털 회로 설계에서 서로 다른 클럭 신호에 의해 동작하는 두 Domain 사이에서 신호나 데이터가 오고 가는 상황을 의미한다.

대표적으로 두 가지 해결책이 있다.

0. Metastability

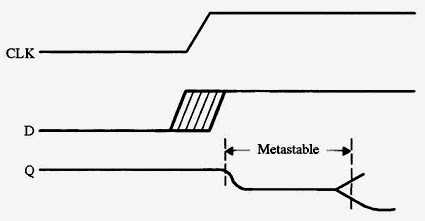

만약, Destination register의 setup/hold timing을 맞추지 못한 경우 register의 출력은 metastable 상태로 전환될 수 있다. 이러한 Metastable 상태에서의 register의 출력은 정상적으로 전환된 후에도 High와 Low의 사이값에 머무른다. 이러한 상황을 Metastability라고 한다.

그러면 파형이 High와 Low 사이에서 오르락 내리락하지만 어디에도 값을 정착하지 못하는 형태로 이어진다. 그러면 이 Register의 출력을 입력으로 하는 다른 register는 0 or 1 or Metastable 으로 될 수 있다.

1. Synchronizer

대표적인 해결책. 2개 이상의 FF를 직렬로 연결한 2-FF Synchronizer를 사용한다. 첫 번째 FF에서 Metastable이 발생하더라도 한 클럭 사이클 동안 불안정한 신호가 안정적으로 변한 시간을 벌어준다. 이로 인해 앞서 설명한 Metastability 에 빠질 확률을 낮출 수 있다.

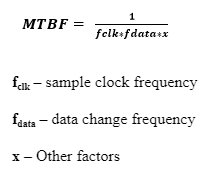

또한 MTBF(Mean Time Between Failures) 라는 지표를 통해 안정성 예측이 가능하다. 동기화에 사용되는 FF의 수가 늘어날수록 MTBF는 급격히 길어지기에, 실패 없이 더 오래 동작이 가능하다. 왜냐하면 앞선 FF에서 발생한 Metastable signal을 1CLK을 기다린 후에 읽기 때문에 충분히 값이 안정될 수 있다.

직역하면, 실패 사이 평균 시간을 의미한다. 어떤 간격으로 실패(고장)가 발생하냐는 의미이다. 그렇기에 MTBF가 크면 고장사이에 간격이 크다.(= 고장이 잘 일어나지 않는다.)가 되는 것이고, MTBF가 작다(= 고장이 자주 발생한다.) 가 된다. 그래서 식에서

$$ MTBF = \frac {1} {f_{clk} * f_{data} * X} $$

>- $f_{clk}$ : Destination Domain의 클럭 주파수

>- $f_{data}$ : 송신 클럭 도메인에서 데이터가 바뀌는 빈도. (신호가 자주 변할수록 확률이 증가하므로 MTBF가 감소함)

>- $X$ : 주로 PVT(Process, Voltage Temperature) 그리고 FF의 Metastable 해소 시간 (τ , metastability resolution time constant)에 의해 결정된다.

2. Dual-Clock FIFO

여러 비트의 데이터를 한 번에 다른 클럭 도메인으로 넘길 때 주로 사용한다. 보내는 쪽(Write)은 Write Clock에 맞춰 FIFO에 데이터를 넣고, 받는 쪽(Read)은 Read Clock에 맞춰 필요할 때 데이터를 빼서 사용하는 구조.

내부적으로는 Write와 Read 포인터를 서로 다른 클럭 도메인으로 넘겨주며 FIFO가 가득 찼는지(full), 비어있는지(empty)를 판단한다. 이 과정에서 포인터 값들을 안전하게 동기화하기 위해 Gray Code와 Synchronizer가 사용된다.

SPI 통신을 예로 들면, 시스템의 메인 클럭(CLK)으로 동작하는 프로세서가 FIFO에 데이터를 쓴다 (wr_en과 Write Data는 CLK에 동기화). 그리고 SPI 통신의 클럭인 SCLK를 사용하는 SPI 컨트롤러는 FIFO에서 데이터를 읽어간다 (rd_en은 SCLK에 동기화). 이처럼 Dual-Clock FIFO를 사용하면 사용자 입장에서는 내부의 복잡한 CDC 처리를 신경 쓰지 않고, 각자의 클럭 도메인에 맞춰 데이터를 쓰고 읽기만 하면 되므로 안전하고 편리하게 여러 비트의 데이터를 서로 다른 클럭 도메인 간에 주고받을 수 있다.

'Circuit Design > 🔥HDL' 카테고리의 다른 글

| [Vivado] IP : FIFO Generator (3) | 2025.11.09 |

|---|---|

| [Vivado] VSCode를 기본 편집기 및 Linting 설정 (1) | 2025.08.25 |

| [Verilog] Verilog를 이용한 AI 설계 응용 및 SoC 설계(3) (0) | 2024.10.09 |

| [Verilog] Verilog를 이용한 AI 설계 응용 및 SoC 설계 (2) (0) | 2024.09.29 |

| [Verilog] Verilog를 이용한 AI 설계 응용 및 SoC 설계 (1) (0) | 2024.09.25 |