다양한 extension 기능이 들어간 VSCode를 VHDL이나 Verilog 같은 RTL 코딩에서도 활용하고 싶어, 제목과 같은 방법을 찾아봤다. 생각보다 간단하다.

먼저 당연하게도 VSCode와 Vivado가 설치되어있어야 한다.

1. Vivado를 켜주자.

2. Vivado 설정 변경

Tools > Text Editor > Current Editor를 기본인 Vivado Text Editor에서 Custom Editor로 변경해주면 된다.

그 후에 VSCode가 설치된 곳의 위치에서 Code.exe 까지 적어준 다음, ` -g [file name]:[line number]`를 뒤에 더해 적어주면 된다.

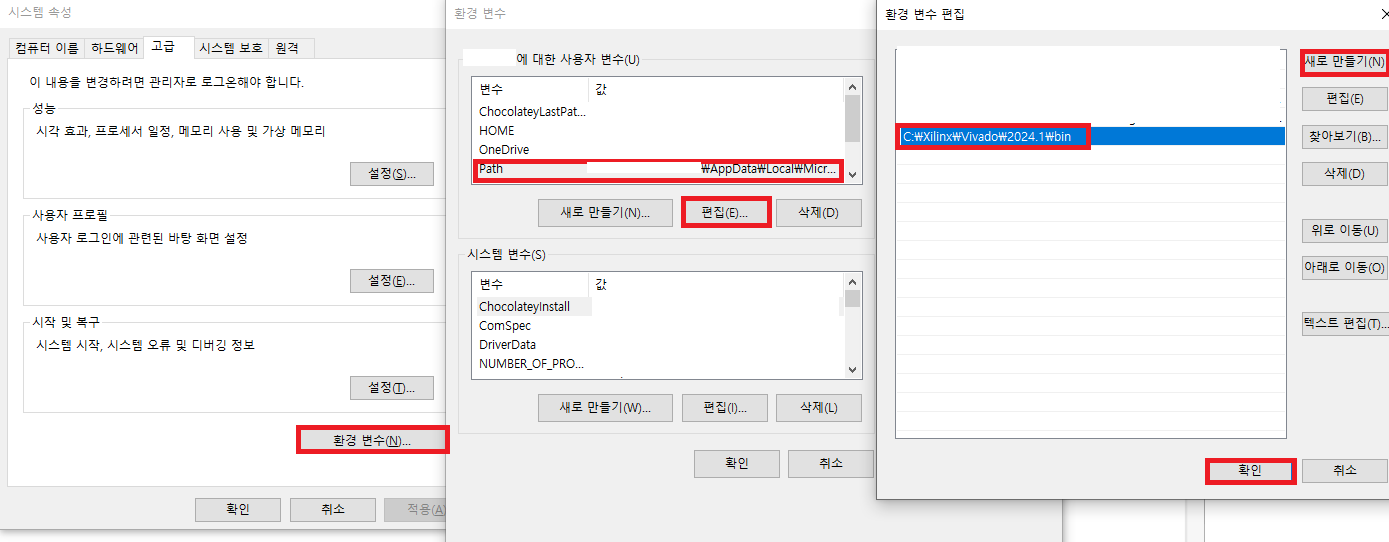

3. 환경 변수 설정

그 후에 환경 변수 > Path 선택 > 편집 > 새로 만들기 > Vivado 내부 bin 파일 주소. 로 적어주고 확인 후 종료.

4. VSCode로 실행 되는 지 확인

그러면 앞으로 Vivado에서 소스 코드를 더블 클릭하면 VSCode로 실행된다.

5. Linting 기능 추가(필요 시)

Linting을 원한다면 위 사진의 Extension을 다운로드 받아준다.

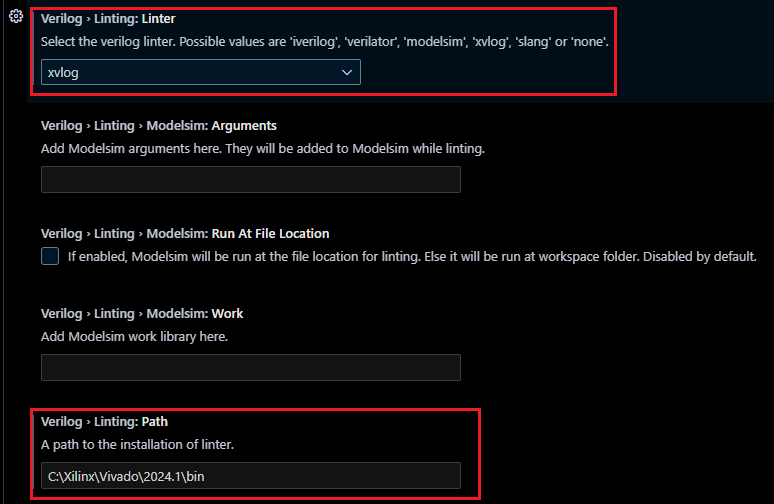

6. Extension Setting

해당 Extension setting에서 위처럼 2개만 바꿔주면 된다.

`xvlog`를 선택하고,

Linting 경로에 환경변수에서 잡은 Vivado 내부 bin 폴더 경로만 입력하면 끝이다.

`Project Manager Extension`을 설치해서, 관리하는 프로젝트 별로 미리 열어두고 작업하는 게 편하기에 나는 그렇게 작업 중이다.

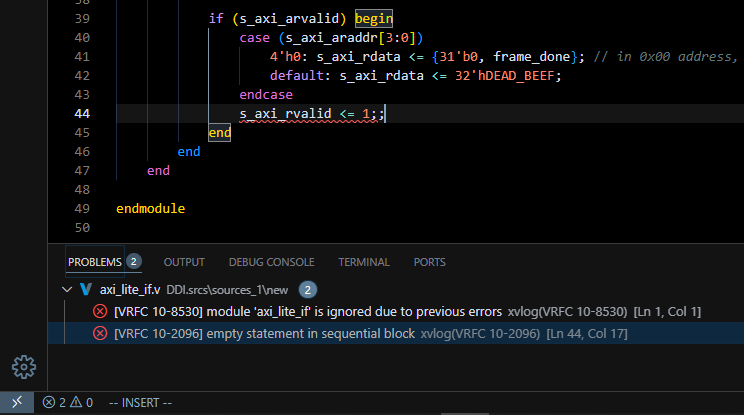

간단하게 보면 위처럼 틀린 문법이 있으면 아래 표시가 된다. 근데 저장해야 반영이 되니 참고하자.

현재 `TerosHDL`이라는 extension도 사용 중이다. 다만 설치 과정이 복잡한 것에 비해 아직 뚜렷한 장점은 체감하지 못했다. 사용해 보며 의미 있는 차이점을 발견하면 추후 포스팅으로 다룰 예정이다.

'Circuit Design > 🔥HDL' 카테고리의 다른 글

| [Vivado] IP : FIFO Generator (3) | 2025.11.09 |

|---|---|

| [설계 용어] CDC(Clock Domain Crossing) (0) | 2025.09.18 |

| [Verilog] Verilog를 이용한 AI 설계 응용 및 SoC 설계(3) (0) | 2024.10.09 |

| [Verilog] Verilog를 이용한 AI 설계 응용 및 SoC 설계 (2) (0) | 2024.09.29 |

| [Verilog] Verilog를 이용한 AI 설계 응용 및 SoC 설계 (1) (0) | 2024.09.25 |