CMOS Inverter(NOT Gate)

NOT Gate는 아래와 같은 회로로 구성됩니다.

위에는 pMOS 아래에는 nMOS를 배치하여 입력을 반전시켜 출력합니다.

A에 0을 입력하면 pMOS는 On, nMOS는 OFF 됩니다. 따라서 출력단인 Y와 VDD가 연결되기 때문에 1로 출력됩니다.

A에 1을 입력하면 pMOS는 OFF, nMOS는 ON 됩니다. 따라서 출력단인 Y와 GND가 연결되기 때문에 0으로 출력됩니다.

Inverter의 심볼과 진리표입니다.

이제 위의 회로를 Cadence Virtuoso를 이용하여 구성하겠습니다.

Virtuoso

먼저 위의 회로도와 같게 pMOS와 nMOS를 배치하고 입력으로 VIN, VDD, VSS를 구성합니다.

나오는 출력은 VOUT으로 잡았습니다.

(pMOS의 W가 2.91u 인 이유는 아래에서 설명)

다음으로 Symbol을 구성하는데, Inverter의 심볼에 맞추어 Stick으로 삼각형을 만들고, Circle로 원을 이어붙여 Symbol을 구성하였습니다.

다음은 구성한 인버터를 테스트하기 위해 Test용으로 Cell을 만들어줍니다.

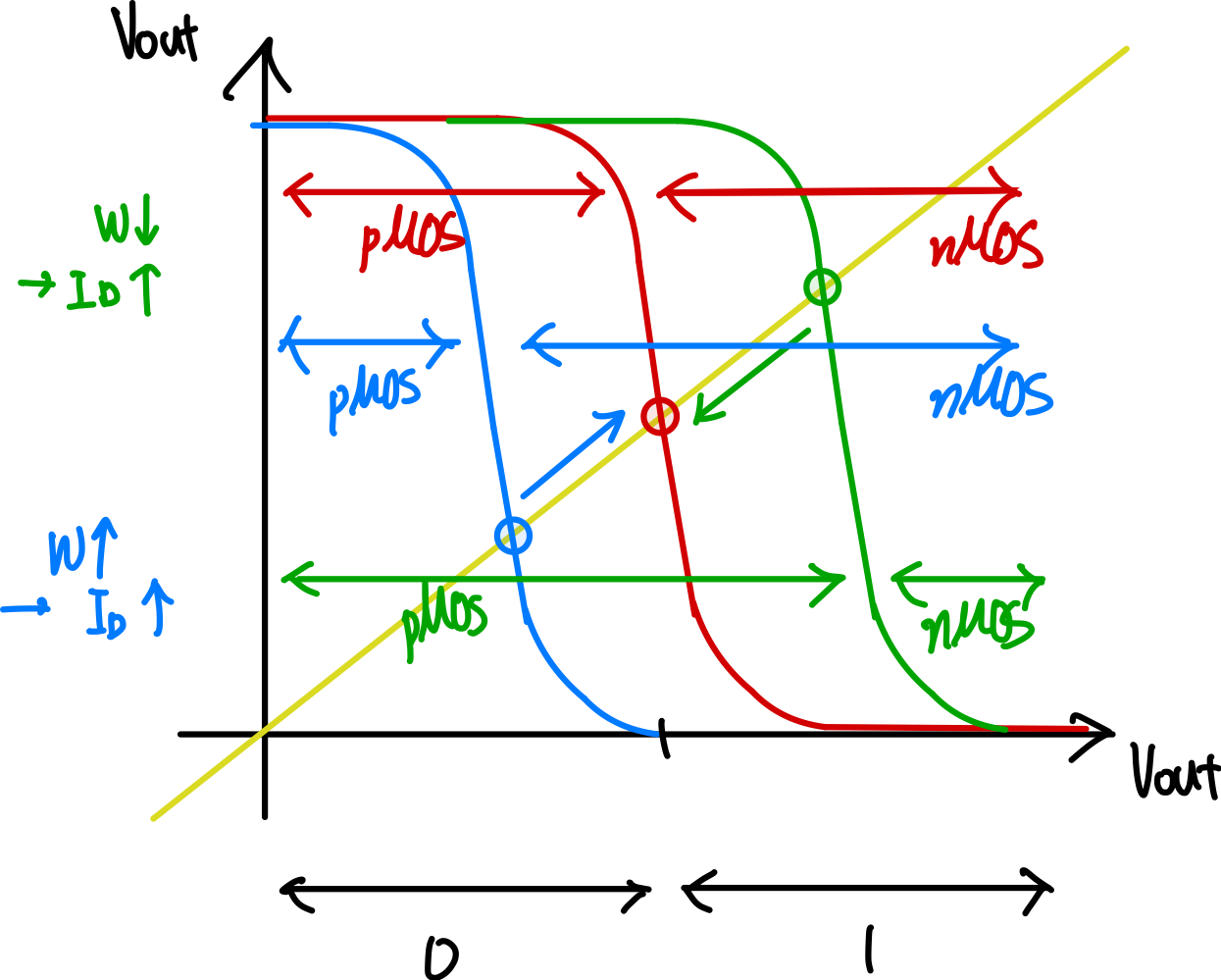

pMOS의 WIDTH 값을 알아내기 위해 'WIDTH'라는 변수로 값을 지정합니다.

WIDTH가 올바르게 나오려면 X축과 Y축이 모두 500이어야 합니다.

올바른 위치를 지정하기 위해 DC SWEEP의 범위를 지속해서 줄여줍니다.

가운데 붉은 그래프가 Ideal한 위치이기 때문에 최대한 가운데 위치한 그래프를 설정합니다

(소수점 두자리 까지)

가까운 값을 WIDTH로 변경합니다.

'Circuit Design > ⚡Layout' 카테고리의 다른 글

| [Virtuoso] 2NOR, 3NOR Layout (0) | 2024.05.07 |

|---|---|

| [Virtuoso] 2NAND, 3NAND Layout (0) | 2024.05.07 |

| [Virtuoso] 3NOR (0) | 2024.04.30 |

| [Virtuoso] 3NAND (0) | 2024.04.30 |

| [Virtuoso] 2NOR (0) | 2024.04.30 |